DesignSparkPCB 基板設計CAD勉強会

シフトレジスタに関して

74xx595 74xx165 74xx164などの

シフトレジスタはD-FF(Dフリップフロップ)を

8段つないだ構成になっています。

まずはD-FFの解説をしておきます。

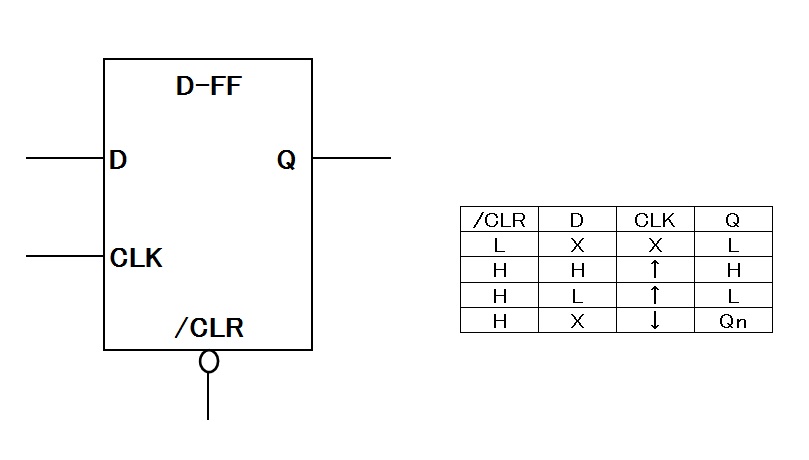

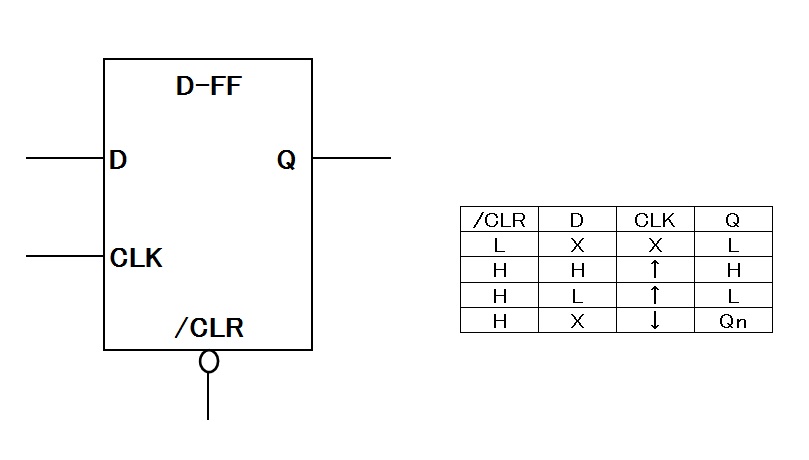

D-FFは入力ピンが「D」「CLK」「/CLR」、

出力ピンは「Q」になります。

74xx74などのD-FFと比較すると

一部機能を割愛した解説になりますが

「/CLR」がリセットです。

「/CLR」が「L」の間は

出力「Q」は常に「L」です。

「/CLR」が「H」になると

「CLK」の立ち上がり毎に

「D」の値が「Q」に出力され

次回の「CLK」の立ち上がりまで保持されます。

「74xx164」や「74xx595」の場合

「CLK」の立ち上がり毎に右方向へ

シフトされる動作になります。

<タイムチャート>

74HC595の構成図です

D-FFが16個使用されています。

上段の8個がシフトレジスタ

下段の8個がラッチ回路になっています。

データシートの「SCK」がクロック

「RCK」がラッチ、「SI」がシリアル(データ)入力

「QH’」はシリアル出力

「QA」「QB」「QC」・・・「QG」「QH」は

パラレル出力になります。

「SCK」(CLK)の立ち上がり毎に

⑧は⑨へ、⑦は⑧へ、⑥は⑦へ

・・・

③⇒④へ、②⇒③へ、①⇒②へそれぞれ

シフトされます。

一方「RCK」(LAT)の立ち上がり毎に

⑫には②の状態が、⑬には③の状態が、

・・・

⑱には⑧の状態が、⑲には⑨の状態が、

出力され保持(ラッチ)されます。

予断になりますが

「/CLR」は負論理(/)が有意のリセット

逆に正論理で有効となりますので

「H」で「EN」と同等の動作となります。

なお「74**595」の「/CLR」で

クリアされるのはシフトレジスタまでです。

ラッチ用D-FFの出力

(パラレル出力「QA」~「QH」)は

クリアされません。

設計ミスの原因となる落とし穴です

電源投入時に出力ハザードで

クレームが発生するアプリケーション

設計時は注意が必要です。

・SP(PS)変換タイミング

・シフトレジスタ

・設計のポイント

参考

RS公式HP DesignSparkPCBの使い方

RS ホームページ

RS公式HP DesignSparkPCBの使い方

窓の社 ホームページ

窓の社HP

無料ガーバーデータ表示ソフト

Online Gerber-Viewer

GC-Prevueの使い方(ユニクラフト)