DesignSparkPCB

基本操作

導入設定

回路設計

基板設計

ライブラリ登録

手配

回路図⇒基板図

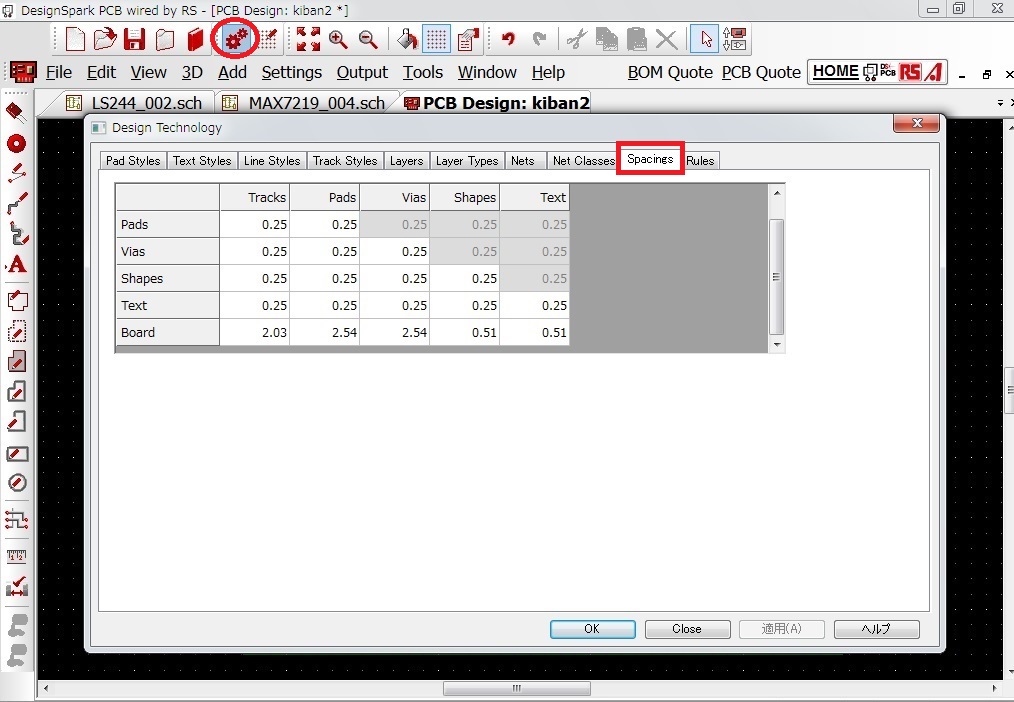

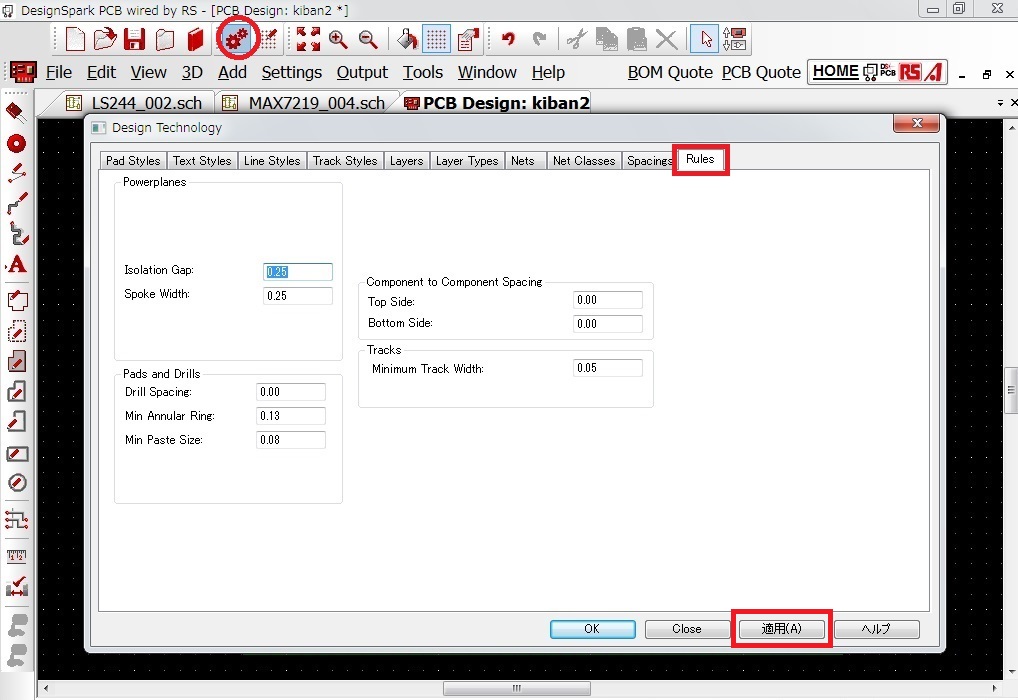

各種設定

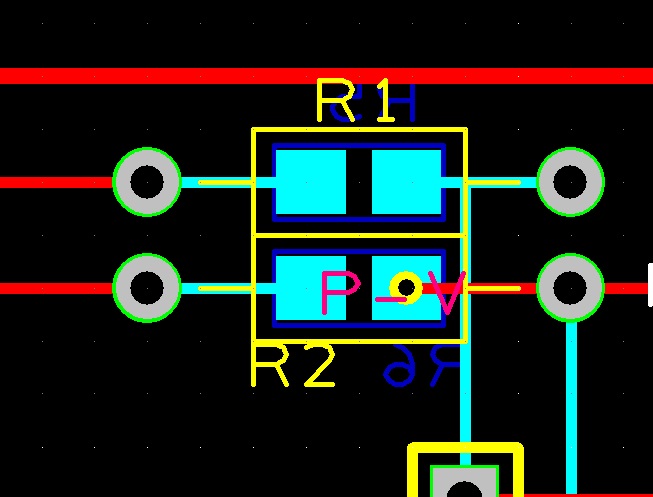

部品の配置

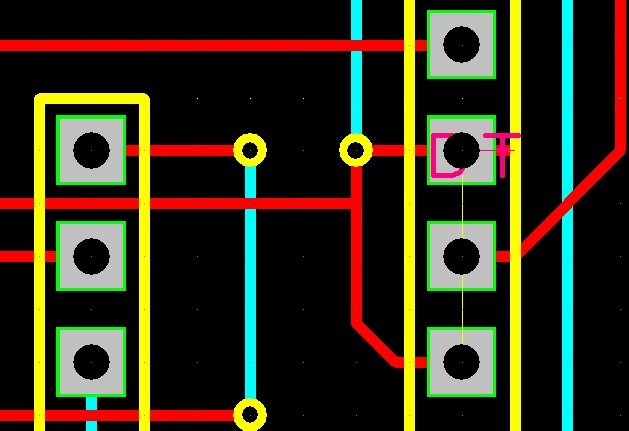

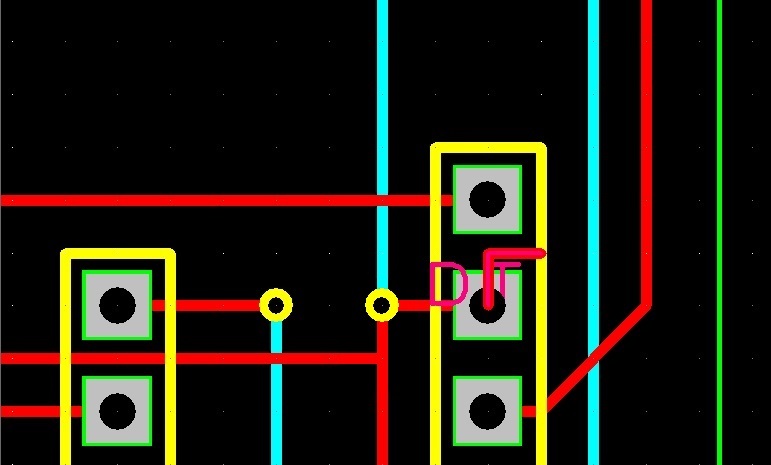

配線

レイヤ表示

文字シルク追加

取付穴

ベタパターン

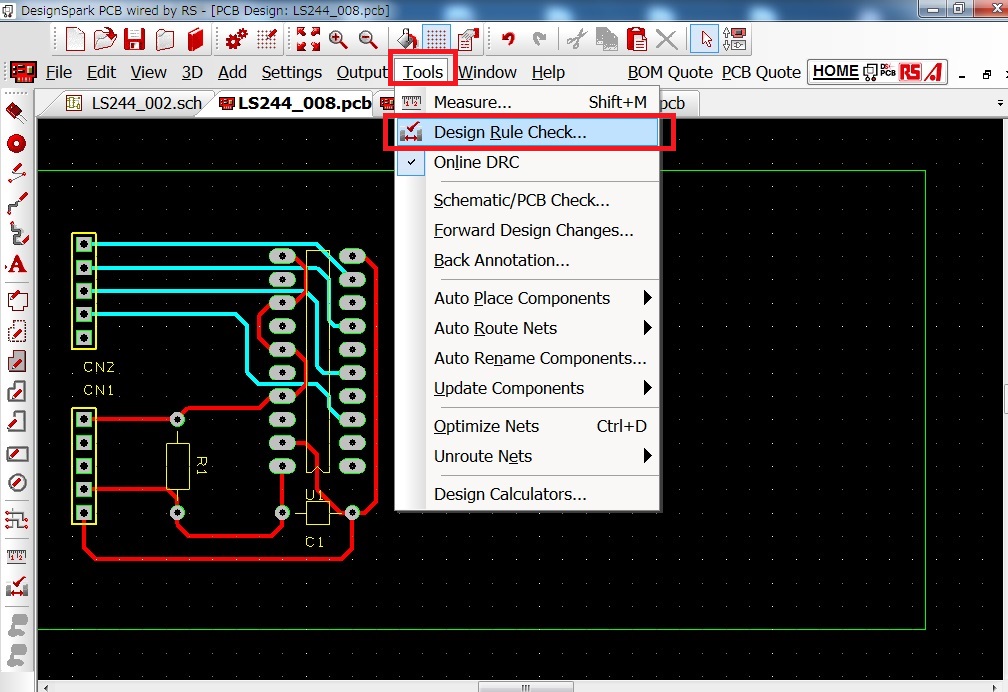

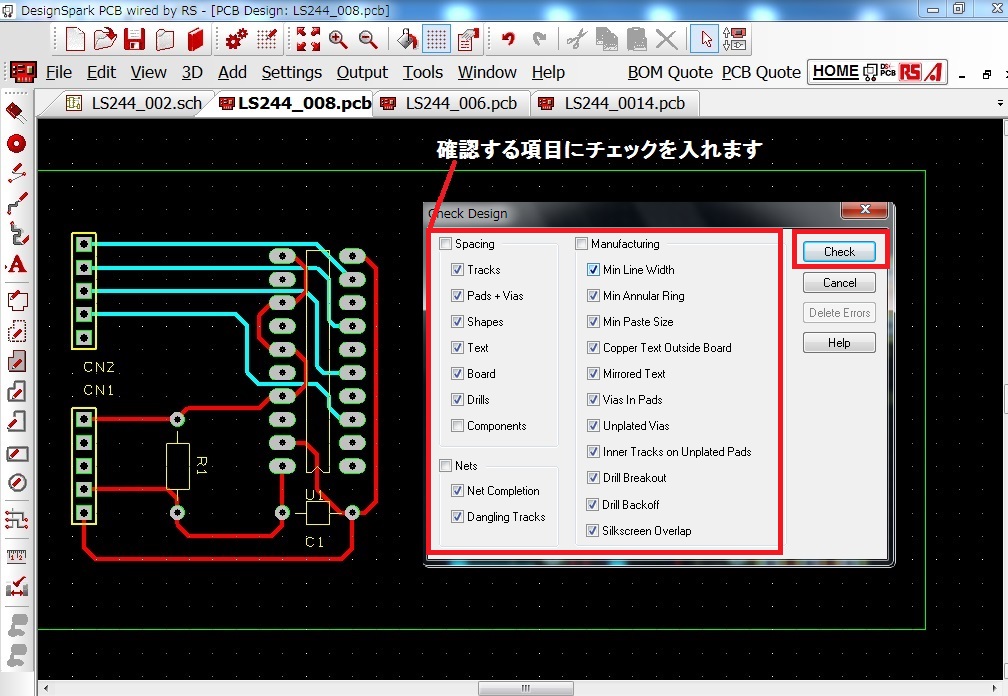

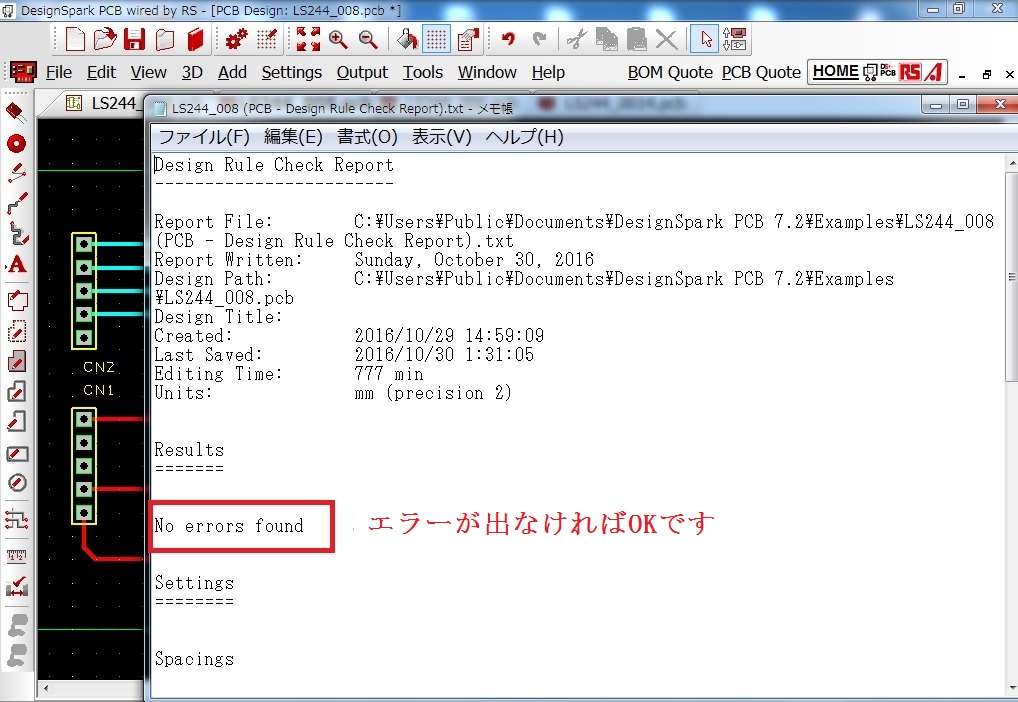

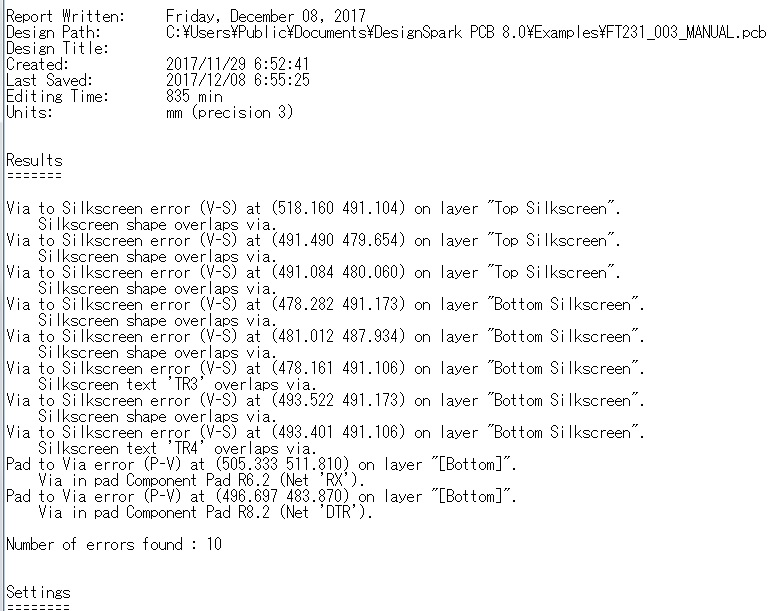

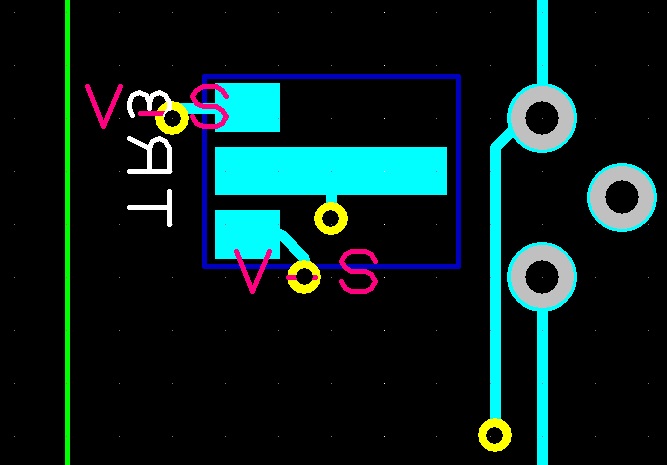

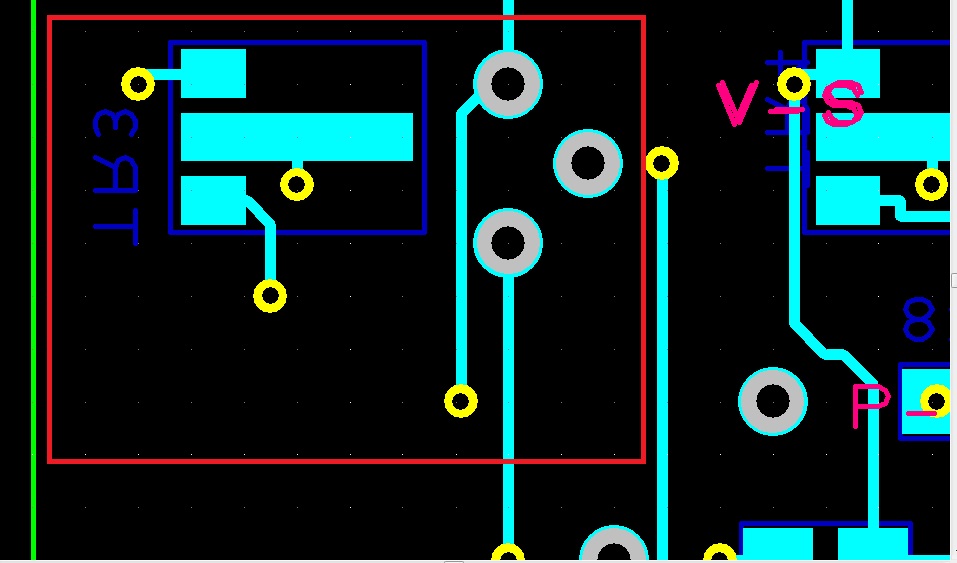

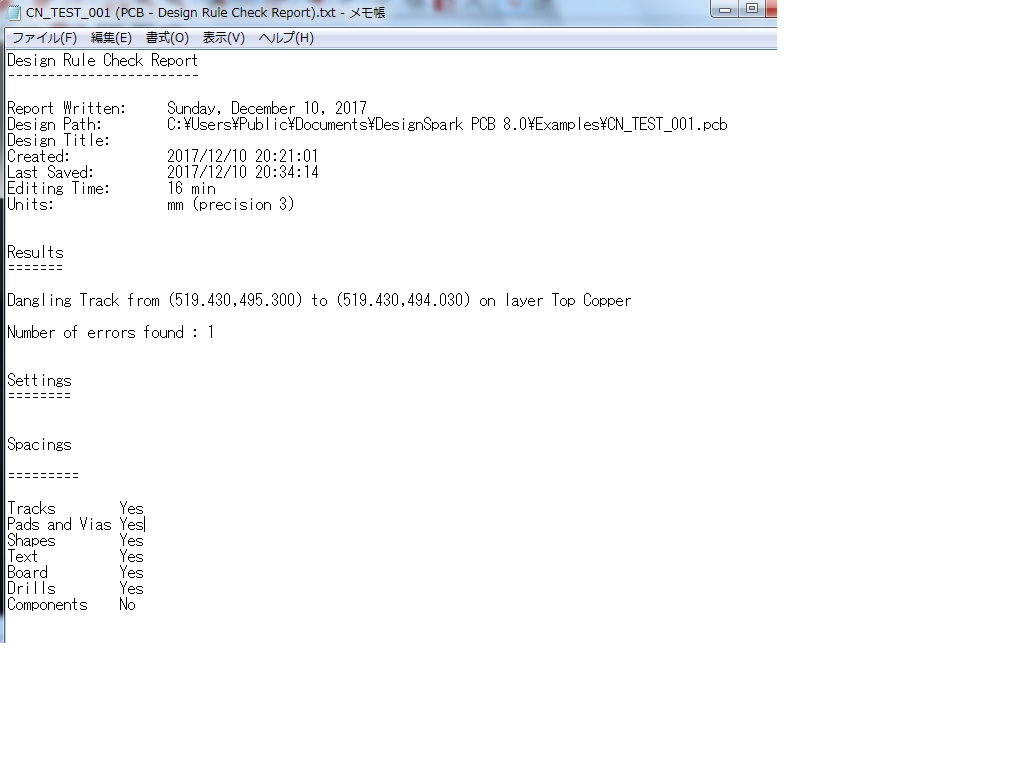

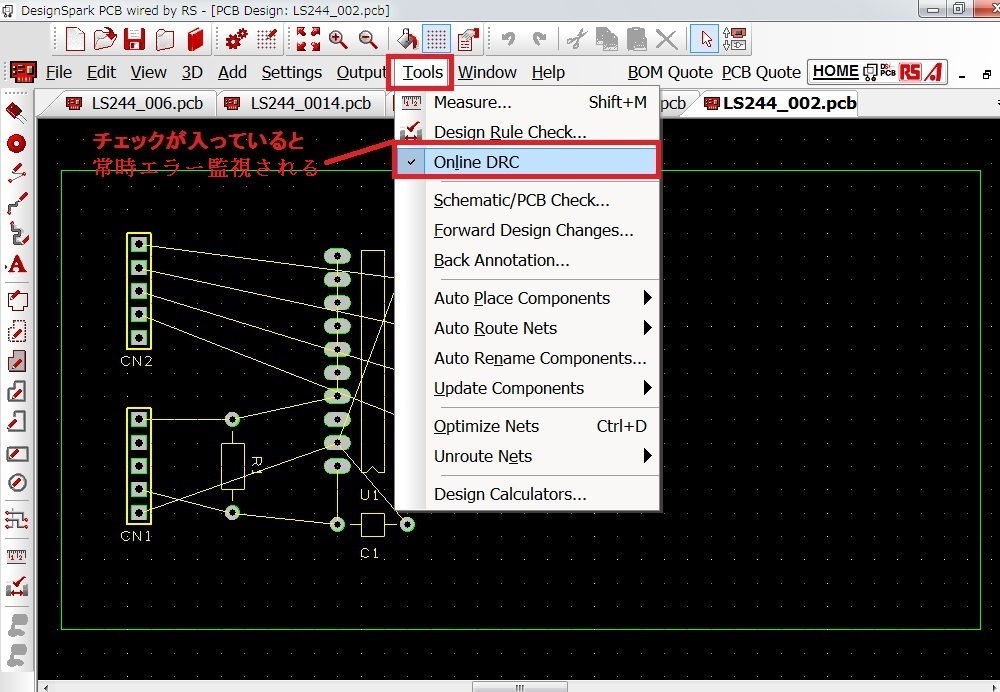

DRCチェック

設計変更の反映

Back Annotation

いきなり基板設計

部品表の作成

回路図⇒基板図

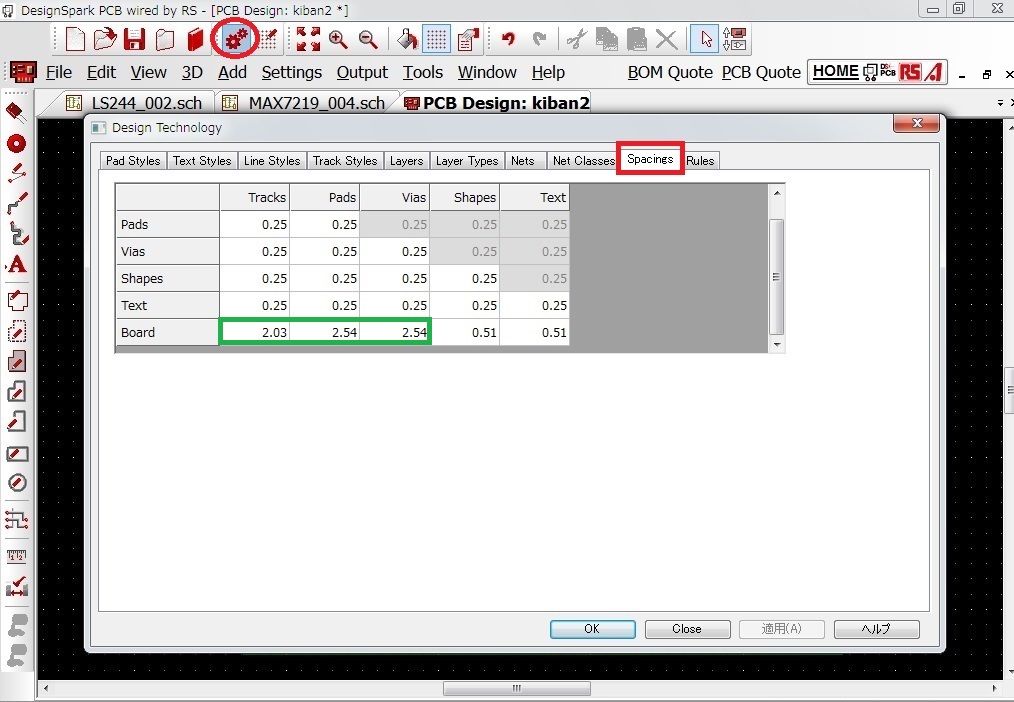

各種設定

部品の配置

配線

レイヤ表示

文字シルク追加

取付穴

ベタパターン

DRCチェック

設計変更の反映

Back Annotation

いきなり基板設計

部品表の作成

基本操作

導入設定

回路設計

基板設計

ライブラリ登録

手配

DesignSparkPCB TOP

北摂ものづくり研究所TOP